# Small-Signal and Temperature Noise Model for MOSFETs

Andreas Pascht, Markus Grözing, Dirk Wiegner, and Manfred Berroth, *Member, IEEE*

**Abstract**—The present CMOS technology provides *n*-channel MOSFETs with a transit frequency beyond 30 GHz, which are attractive for RF integrated circuits, e.g., low-noise amplifiers. This paper presents an improved deembedding procedure for extraction of parasitic elements of MOSFETs. The extraction determines the intrinsic elements of the small-signal equivalent circuit. As a result, a new method to determine the gate capacitance is presented. This deembedding procedure is based on an analytical solution of the equations and facilitates the determination of the elements at any specific frequency. Moreover, a temperature noise model is presented, which is based on the small-signal equivalent circuit with an analytical description of the channel noise. This enables a complete noise modeling of all four noise parameters and the determination of the dominant noise sources. Finally, the noise-figure measurements are compared with the simulation results.

**Index Terms**—Deembedding, MOSFET, temperature noise model.

## I. INTRODUCTION

DECREASING channel length and consequently increasing transit frequency allow for the use of MOSFETs in RF-CMOS circuits and, thus, provide the fabrication of systems-on-a chip. For circuit development, precise small-signal and noise equivalent circuits of the devices are required. Due to the resistive substrate losses of RF MOSFETs, a separation of interconnection network and intrinsic device is important (see Section II). Therefore, a two-step deembedding procedure is proposed to separate intrinsic transistor elements to obtain a valid transistor model for circuit simulation. Hereby, parasitic parallel elements introduced by the pads are first determined from an additional test structure, whereas series elements are then deduced from measurements at passive device biasing conditions. A new method for the determination of the channel resistance and gate capacitance is presented (i.e., cold modeling, see Section III). The intrinsic elements can be obtained after separation of the parasitic elements (hot modeling, see Section IV).

A temperature noise model capable of predicting all four noise parameters at any frequency, any temperature, and operating point is presented (see Sections V and VI).

## II. SMALL-SIGNAL EQUIVALENT CIRCUIT

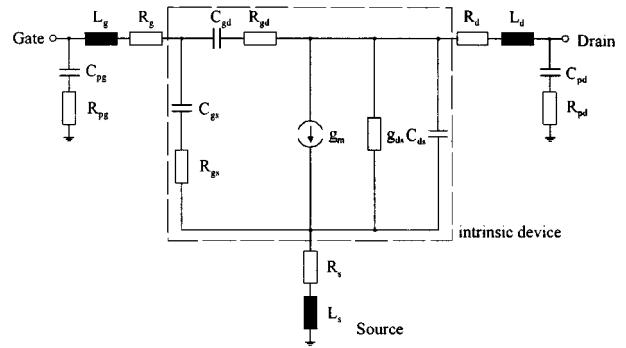

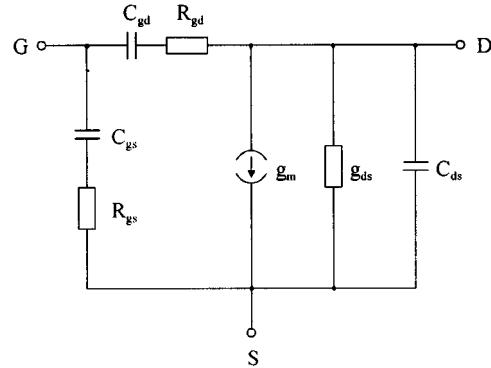

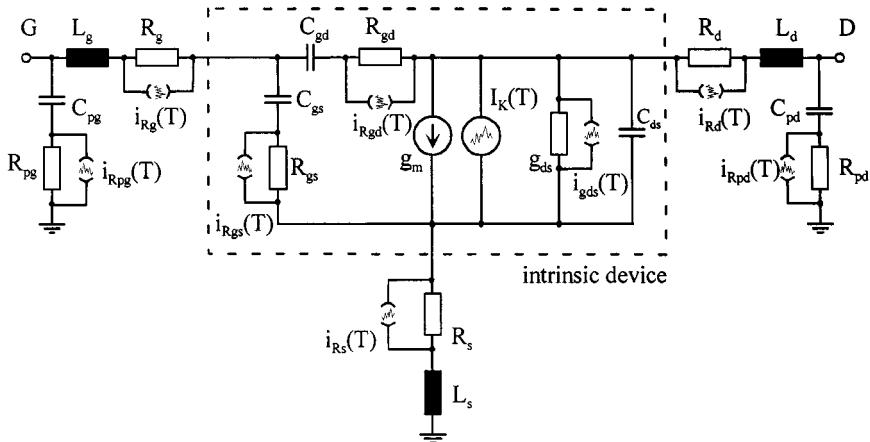

Fig. 1 shows the small-signal equivalent circuit of the MOSFET with common source configuration used for the

Manuscript received May 13, 2001.

The authors are with the Institute of Electrical and Optical Communication Engineering, University of Stuttgart, D-70569 Stuttgart, Germany (e-mail: a.pascht@gmx.de).

Publisher Item Identifier 10.1109/TMTT.2002.801339.

Fig. 1. Small-signal equivalent circuit of a MOSFET.

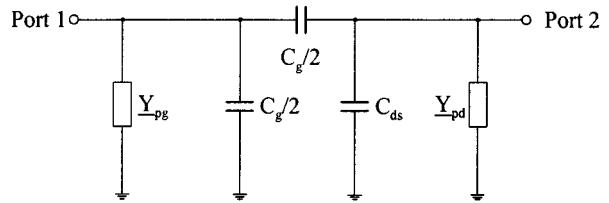

Fig. 2. Equivalent circuit of the MOSFET device for zero drain voltage and gate voltage below pinchoff.

deembedding procedure [1]. The intrinsic transistor is embedded by series resistors  $R_g$ ,  $R_d$ , and  $R_s$  and series inductors  $L_g$ ,  $L_d$ , and  $L_s$  representing the interconnection lines. In addition, the parasitics of the pad due to substrate losses are modeled by the capacitors  $C_{pg}$  and  $C_{pd}$  in series with the resistors  $R_{pg}$  and  $R_{pd}$ . The small-signal equivalent circuit can be expanded with a substrate network if necessary. The two-step method separates these elements from the intrinsic device.

## III. COLD MODELING

First of all, the four elements, which are characterizing the pads ( $C_{pg}$ ,  $C_{pd}$ ,  $R_{pg}$ , and  $R_{pd}$ ), are derived from a measurement of a test structure with the same metallization as the real structure, but without connected transistor (open structure) neglecting any coupling between gate and drain [2]. In the following, the gate and drain pads are represented by  $\underline{Y}_{pg}$  and  $\underline{Y}_{pd}$ . The gate capacitance  $C_g$  is determined for the derivation of the still missing elements. Fig. 2 shows the valid small-signal equivalent circuit for a gate voltage below pinchoff and at zero drain voltage. In this case the transistor can be modeled by capacitors only. The circuit consists of the pads with  $\underline{Y}_{pg}$  and  $\underline{Y}_{pd}$ , a gate capacitance subdivided to source and drain, a coupling capacitance between gate and drain, which is neglected

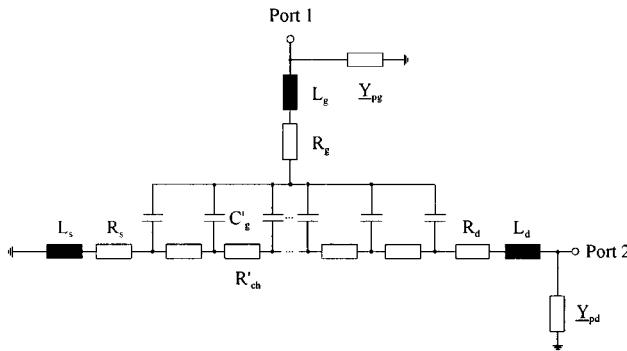

Fig. 3. Equivalent circuit of the MOSFET device for zero drain voltage and gate voltage above pinchoff.

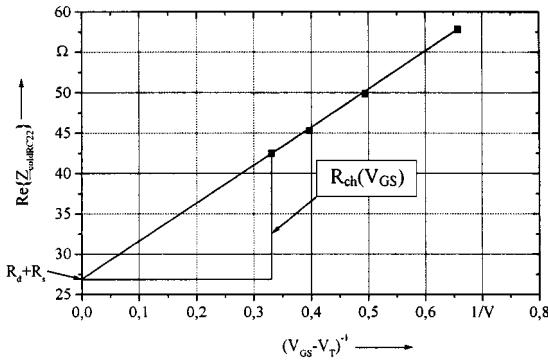

Fig. 4. Determination of the channel resistor  $R_{ch}$ .

in the following, and a channel capacitance between source and drain.

The gate capacitance can be derived from the  $\underline{Y}$ -parameters of the small-signal equivalent circuit of Fig. 2 as follows:

$$C_g = \frac{2 \left( \text{Im} \left\{ \underline{Y}_{11\text{cold}C} \right\} + \text{Im} \left\{ \underline{Y}_{12\text{cold}C} \right\} - \text{Im} \left\{ \underline{Y}_{pg} \right\} \right)}{\omega} \quad (1)$$

Fig. 3 shows the equivalent circuit, which is valid for a gate voltage above pinchoff and at zero drain voltage [3]. The intrinsic device is modeled through a distributed channel resistance  $R'_{ch}$  and a distributed gate capacitance  $C'_g$ .

The device is measured at different gate voltages for zero drain voltage. The channel resistance  $R_{ch}$  is determined from the real part of the  $\underline{Z}_{22}$ -parameter by extrapolating the sum of  $R_d$  and  $R_s$  at large gate voltages according to the following:

$$\text{Re} \{ \underline{Z}_{22} \} = R_d + R_s + R_{ch} = R_d + R_s + \frac{1}{\beta} \frac{1}{(V_{GS} - V_T)} \quad (2)$$

Fig. 4 shows the determination of the channel resistance. The points in Fig. 4 are the measured values at different gate voltages and the line is the extrapolation, which allows the determination of the sum of  $R_d$  and  $R_s$  and thereby the calculation of the channel resistor  $R_{ch}$ .

For the verification of the presented deembedding procedure, measurements were performed with a standard 0.35- $\mu\text{m}$  CMOS

Fig. 5. High-frequency equivalent circuit of the intrinsic device.

process from the JESSI Project. The measurements were performed with a microwave probing system in the frequency range of 50 MHz–20 GHz. The method requires measurement results of an open structure and of an active device at different operating points for hot and cold modeling.

The good agreement of measurement and interpolation justifies the equivalent circuit for zero drain voltage and gate voltage above pinchoff (Fig. 3).

With the knowledge of the gate capacitance  $C_g$ , channel resistance, and complete set of  $\underline{Z}$ -parameters for the equivalent circuit of Fig. 3, the remaining parasitic elements  $R_g$ ,  $R_s$ ,  $R_d$ ,  $L_g$ ,  $L_s$ , and  $L_d$  can be derived as follows:

$$\underline{Z}_{11} = R_g + R_s + \frac{R_{ch}}{3} + j \left[ \omega(L_g + L_s) - \frac{1}{\omega C_g} \right] \quad (3)$$

$$\underline{Z}_{12} = \underline{Z}_{21} = R_s + \frac{R_{ch}}{2} + j\omega L_s \quad (4)$$

$$\underline{Z}_{22} = R_d + R_s + R_{ch} + j\omega[L_d + L_s]. \quad (5)$$

The deembedding matrix for the series elements used in Fig. 1 is formulated as follows:

$$[\underline{Z}_s] = \begin{bmatrix} \underline{Z}_{11} - \frac{R_{ch}}{3} + j\frac{1}{\omega C_g} & \underline{Z}_{12} - \frac{R_{ch}}{2} \\ \underline{Z}_{21} - \frac{R_{ch}}{2} & \underline{Z}_{22} - R_{ch} \end{bmatrix}. \quad (6)$$

#### IV. HOT MODELING

Knowing all parasitic elements, the measured  $S$ -parameters can be deembedded from the parasitics, and the intrinsic  $\underline{Y}_i$ -parameters can be deduced as follows:

$$[\underline{Y}_i] = \left[ ([\underline{Y}_a] - [\underline{Y}_{pad}])^{-1} - [\underline{Z}_s] \right]^{-1}. \quad (7)$$

$\underline{Y}_i$  represent the  $\underline{Y}$ -parameters of the intrinsic device, which are calculated via matrix operations, where  $\underline{Y}_a$  are the  $\underline{Y}$ -parameters of the measured device at the reference plane.

Fig. 5 shows the small-signal equivalent circuit of the intrinsic device with all parasitic elements subtracted. The

TABLE I

ELEMENT VALUES FOR AN OPERATION POINT IN SATURATION

( $V_{DS} = V_{GS} = 2$  V) FOR A CHANNEL WIDTH OF  $w = 43.75$   $\mu\text{m}$

AND A CHANNEL LENGTH OF  $l = 0.35$   $\mu\text{m}$

| Element  | Value              |

|----------|--------------------|

| $R_{pd}$ | $0.8 \Omega$       |

| $R_{pg}$ | $1.3 \Omega$       |

| $C_{pd}$ | $110.4 \text{ fF}$ |

| $C_{pg}$ | $114.1 \text{ fF}$ |

| $L_d$    | $10.1 \text{ pH}$  |

| $L_g$    | $26.7 \text{ pH}$  |

| $L_s$    | $-18.5 \text{ pH}$ |

| $R_d$    | $14.7 \Omega$      |

| $R_g$    | $35.5 \Omega$      |

| $R_s$    | $14.5 \Omega$      |

| $R_{gs}$ | $11.1 \Omega$      |

| $C_{gs}$ | $51.5 \text{ fF}$  |

| $C_{gd}$ | $14.1 \text{ fF}$  |

| $C_{ds}$ | $33.5 \text{ fF}$  |

| $g_{ds}$ | $1.3 \text{ mS}$   |

| $g_m$    | $10.3 \text{ mS}$  |

| $\tau$   | $679.3 \text{ fs}$ |

so-called “hot-modeling” allows the calculation of the elements by the  $\underline{Y}$ -parameters of the equivalent circuit as follows:

$$R_{gs} = \text{Re} \left\{ \frac{1}{\underline{Y}_{11} + \underline{Y}_{12}} \right\} \quad (8)$$

$$R_{gd} = -\text{Re} \left\{ \frac{1}{\underline{Y}_{12}} \right\} \quad (9)$$

$$C_{gs} = -\frac{1}{\omega} \frac{1}{\text{Im} \left\{ \frac{1}{\underline{Y}_{11} + \underline{Y}_{12}} \right\}} \quad (10)$$

$$C_{gd} = \frac{1}{\omega} \frac{1}{\text{Im} \left\{ \frac{1}{\underline{Y}_{12}} \right\}} \quad (11)$$

$$C_{ds} = \frac{1}{\omega} \text{Im} \left\{ \underline{Y}_{12} + \underline{Y}_{22} \right\} \quad (12)$$

$$g_{ds} = \text{Re} \left\{ \underline{Y}_{12} + \underline{Y}_{22} \right\} \quad (13)$$

$$g_m = \frac{|\underline{Y}_{12} - \underline{Y}_{21}|}{|\underline{Y}_{11} + \underline{Y}_{12}| \text{Im} \left\{ \frac{1}{|\underline{Y}_{11} + \underline{Y}_{12}|} \right\}} \quad (14)$$

$$\tau = -\frac{1}{\omega} \text{arc} \left( \frac{j(\underline{Y}_{12} - \underline{Y}_{21})}{(\underline{Y}_{11} + \underline{Y}_{12}) \text{Im} \left\{ \frac{1}{(\underline{Y}_{11} + \underline{Y}_{12})} \right\}} \right). \quad (15)$$

Table I shows the so-determined element values of an operating point in the saturation region for a device with a channel

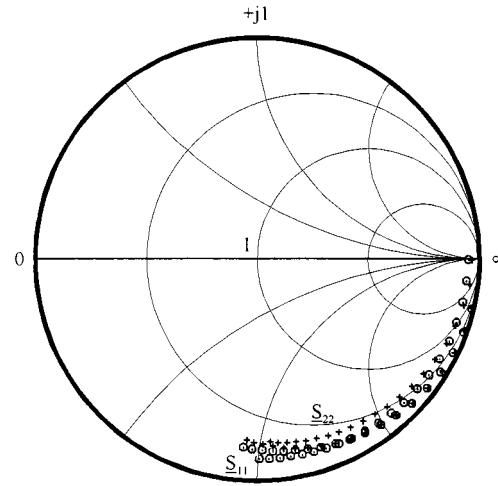

Fig. 6. Input and output reflection factors  $\underline{S}_{11}$  and  $\underline{S}_{22}$  of the intrinsic device in saturation (measurement: crosses, simulation: circles).

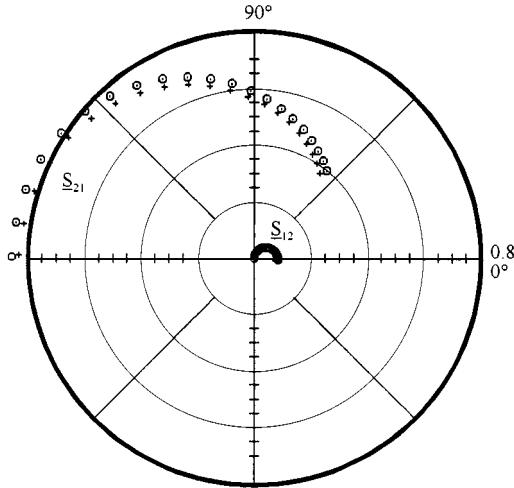

Fig. 7. Forward and reverse transmission factors  $\underline{S}_{21}$  and  $\underline{S}_{12}$  of the intrinsic device in saturation (measurement: crosses, simulation: circles).

width of  $w = 43.75$   $\mu\text{m}$ . The source inductance  $L_s$  is negative due to a numeric extraction accuracy problem, which can be solved using [4].

Fig. 6 shows input and output reflection ( $\underline{S}_{11}$  and  $\underline{S}_{22}$ ) of the intrinsic deembedded device at saturation. Measured values are depicted as crosses and simulation results as circles.

$\underline{S}_{11}$  and  $\underline{S}_{22}$  show good agreement with small deviations for high frequencies. In this case, the mean-square deviation is 1.9% for  $\underline{S}_{11}$  and 4.5% for  $\underline{S}_{22}$ . Fig. 7 shows the transmission factors (forward and reverse)  $\underline{S}_{21}$  and  $\underline{S}_{12}$  of the intrinsic transistor in a polar plot.

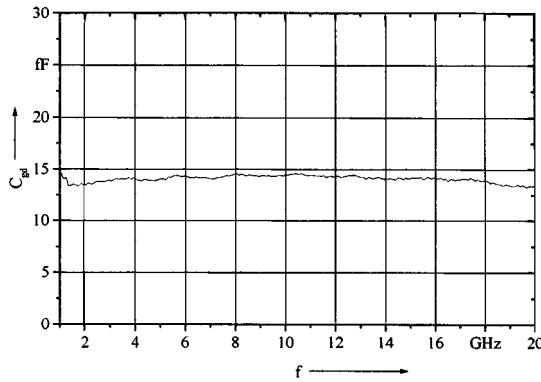

Small deviations occur for  $\underline{S}_{21}$  and  $\underline{S}_{12}$  with a mean-square deviation of 1.3% for  $\underline{S}_{21}$  and 10.2% for  $\underline{S}_{12}$ . To verify the validity of the equivalent circuits used at every step of the deembedding procedure, the frequency dependence of the elements has to be checked [5]. If there is no frequency dependence, the equivalent circuit is valid. As the deembedding procedure is frequency independent, the element values can be calculated at every frequency point. To illustrate this, Fig. 8 shows the frequency dependence of the capacitance  $C_{gd}$  in the frequency range of 0–20 GHz.

Fig. 8. Intrinsic capacitance  $C_{gd}$  versus the frequency.

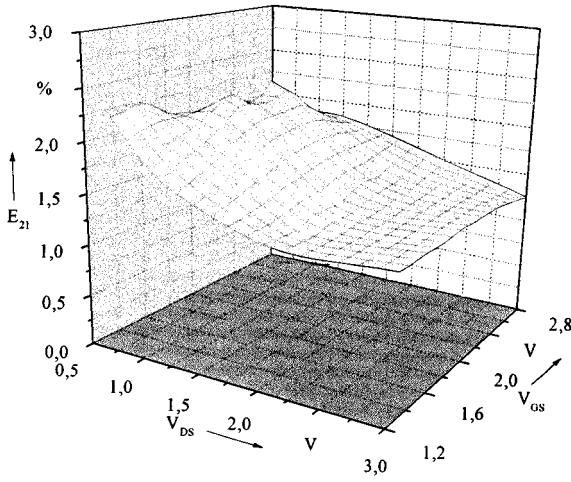

Fig. 9. Error term of the forward transmission factor  $E_{21}$  versus the operating point.

The extracted value of the intrinsic element  $C_{gd}$  shows almost no frequency dependence up to 20 GHz. Fig. 9 shows as an example the error term of the forward transmission factor  $E_{21}$  to demonstrate the independence of the extraction method for the operating point.

## V. NOISE MODELING

We propose a noise model based on the equivalent-circuit model of Fig. 1 including all intrinsic noise sources. In addition to the thermal noise of the resistors, the channel noise of the device is taken into account, which can be determined analytically or by a single measurement.

### A. Small-Signal Equivalent Noise Circuit

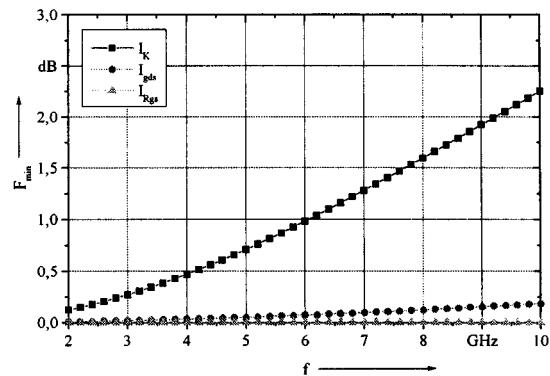

We use a temperature noise model of the MOSFET for device characterization similar to [6]. The first step is the allocation of the intrinsic noise sources. In contrast to the already existing modeling approaches, the complete small-signal equivalent circuit of the MOS transistor, including all parasitic elements of the pads and interconnection lines, is used. Fig. 10 shows the proposed small-signal equivalent noise circuit of the MOSFET. The thermal noise of each resistor is described by the adequate noise current source. The noise generated by the channel current is modeled by the noise current source  $I_K$ .

### B. Noise Sources

Typically, two noise sources are needed to characterize a noisy two-port [7]. As the small-signal equivalent circuit already describes the linear two-port characteristics, only the additional noise sources at the input and output are required to describe the four noise parameters of the device. As the gate is isolated from the channel, only thermal noise sources are considered at the input port. All resistors generate uncorrelated thermal noise according to their absolute temperature  $T_0$ , which is expressed through the effective value of the noise current  $i_R$  [see (16)] [8]

$$i_R^2 = \frac{4kT_0\Delta f}{R}. \quad (16)$$

$k$  is the Boltzmann constant,  $T_0$  is the ambient temperature,  $\Delta f$  is the frequency bandwidth of interest, and  $R$  is any resistor of the equivalent circuit.

In addition to the thermal noise, we use only one noise source in parallel to the drain current source at the output. The diffusion noise is caused by the drain current and can be derived by an analytical equation (17), as described in [9]

$$i_K^2 = 4kT_0\Delta f \mu_{\text{eff}}^2 c_g^2 \frac{w^2}{l^2 I_D} \cdot \left[ (V_{GS} - V_T)^2 V_{DS\text{sat}} - (V_{GS} - V_T) V_{DS\text{sat}}^2 + \frac{1}{3} V_{DS\text{sat}}^3 \right] - 4kT_0\Delta f \frac{w c_g \mu_{\text{eff}}}{l^2 E_c} \left[ (V_{GS} - V_T) V_{DS\text{sat}} - \frac{1}{2} V_{DS\text{sat}}^2 \right]. \quad (17)$$

$\mu_{\text{eff}}$  is the effective electron mobility,  $c_g$  is the gate capacitance per unit area,  $w$  is the channel width,  $l$  is the channel length,  $I_D$  is the drain current,  $V_{GS}$  is the gate-to-source voltage,  $V_T$  is the threshold voltage,  $V_{DS\text{sat}}$  is the drain-to-source voltage in saturation and  $E_c$  is the electric field at which electrons reach velocity saturation.

Equation (17) has to be replaced through (18) in case of an operating point in the triode region

$$i_K^2 = 4kT_0\Delta f \mu_{\text{eff}}^2 c_g^2 \frac{w^2}{l^2 I_D} \cdot \left[ (V_{GS} - V_T)^2 V_{DS} - (V_{GS} - V_T) V_{DS}^2 + \frac{1}{3} V_{DS}^3 \right] - 4kT_0\Delta f \frac{w c_g \mu_{\text{eff}}}{l^2 E_c} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right]. \quad (18)$$

$V_{DS}$  is the drain-to-source voltage.

On the other hand, the equivalent noise current  $I_K$  can be determined by a single noise measurement at any source impedance. As this is valid for each frequency, a verification of the model can also be done with measurements across a broad frequency range.

No additional correlation between the noise sources has to be calculated. The correlation is given through the transfer function of the device.

Fig. 10. Small-signal equivalent circuit of the MOSFET extended for noise modeling.

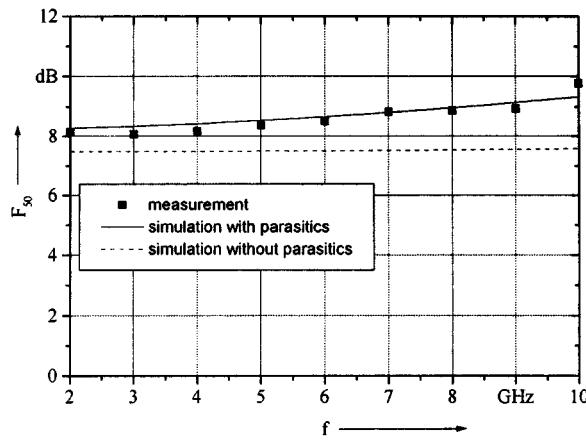

Fig. 11. Comparison of the measured noise figure of the MOSFET with simulation at a source impedance of  $50 \Omega$ .

## VI. NOISE CHARACTERIZATION

Fig. 11 shows simulation (performed with Agilent ADS) and measurement of the MOSFET's noise figure at a source impedance of  $50 \Omega$ , which can be easily performed in addition to  $S$ -parameter measurements.

Additionally, Fig. 11 shows the simulation of the device without pads and interconnection lines, resulting in a reduction of the noise figure of more than 1 dB.

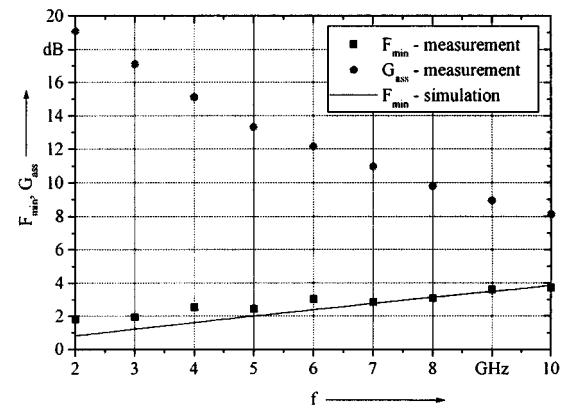

The very large value of the noise figure is due to the source mismatch of the device. The minimum noise figure was measured additionally using an automatic tuned measurement system (Fig. 12). Due to a still mismatched source of the measurement system, there is a difference between measurement and simulation at very low noise figures. In addition, the experimental data of the associated gain are included, demonstrating the RF performance of the device. For comparison with measurements or other devices, the four noise parameters of a noisy two-port can be determined by simulation.

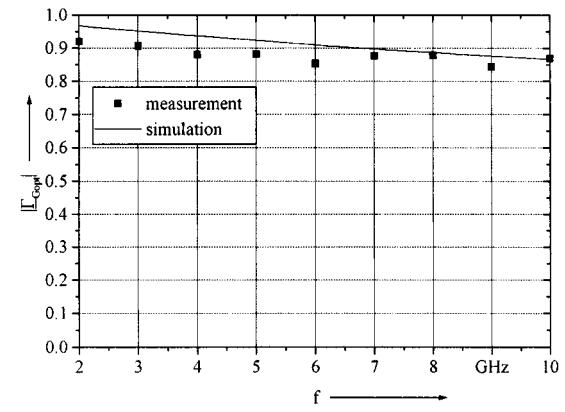

Fig. 13 shows the absolute value of the optimum generator reflection factor. This is the second noise parameter that can also be determined by a tuned noise measurement.

The large absolute value of the optimum generator reflection factor explains the great difference between the noise figure at  $50 \Omega$  and for minimum noise matching.

Fig. 12. Measurement of the associated gain (dots) and minimum noise figure (squares) of the MOSFET in comparison with noise model simulations.

Fig. 13. Comparison of the measured absolute value of the optimum generator reflection factor of the MOSFET with simulation (measurement: squares).

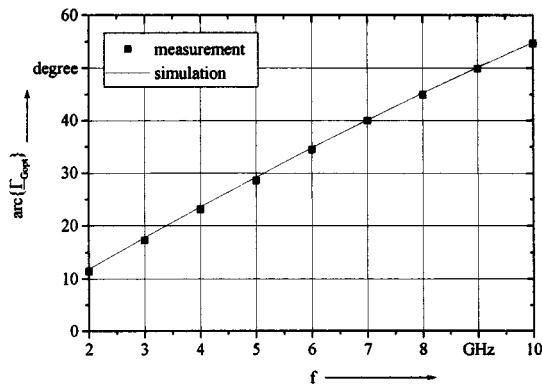

The comparison between measurement and simulation of the third noise parameter is shown in Fig. 14. It is the phase of the optimum generator reflection factor that can be modeled in good agreement to the measurements.

With the knowledge of the absolute value and the phase of the optimum generator reflection factor, the noise matching of the device can be achieved using standard circuit simulators.

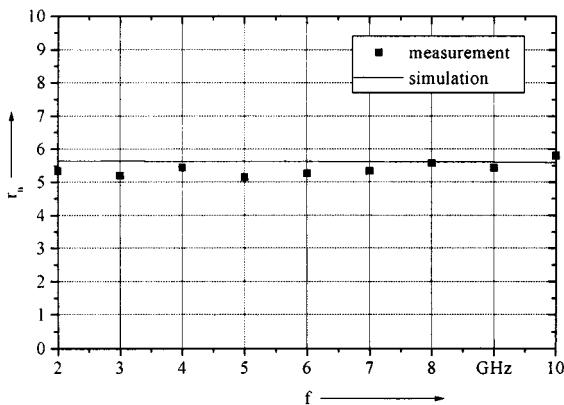

The last noise parameter, i.e., the equivalent noise resistance, is shown in Fig. 15.

Fig. 14. Comparison of the measured phase of the optimum generator reflection factor of the MOSFET with simulation (measurement: squares).

Fig. 15. Comparison of the measured equivalent noise resistance of the MOSFET with simulation (measurement: squares).

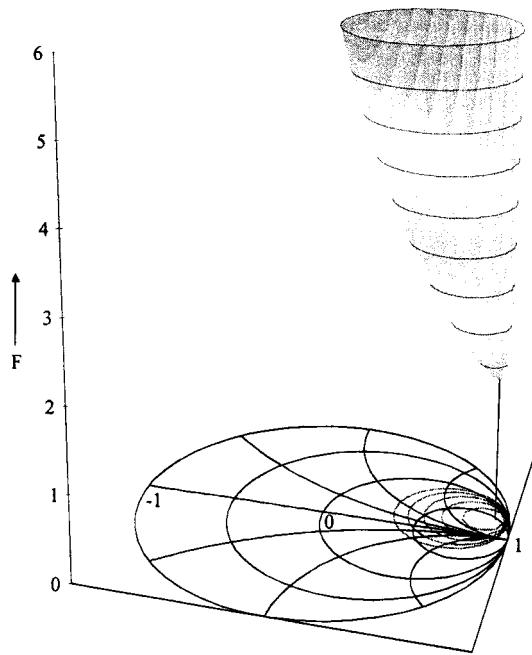

Fig. 16. Measurement of the noise paraboloid of the used MOSFET.

Fig. 16 shows the measured noise paraboloid of the MOSFET, which is determined by all four noise parameters.

Fig. 17. Sensitivity analysis of the intrinsic noise sources at noise matching.

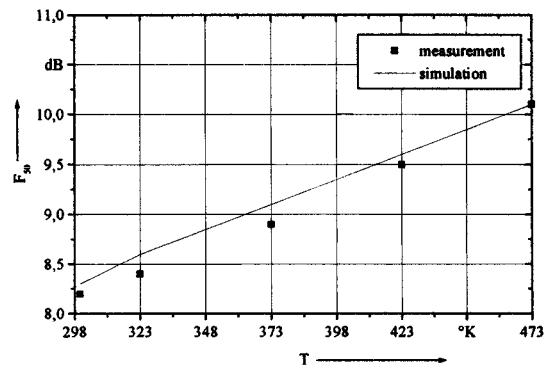

Fig. 18. Comparison of the measured noise figure (dots) with simulation (line) versus temperature ( $V_{\text{GS}} = V_{\text{DS}} = 2$  V).

The very high equivalent noise resistance is responsible for the strong increase of the noise figure in case of a source mismatch. Therefore, the source matching is much more critical in MOSFET circuits. One key feature of the noise equivalent-circuit model is the ability to identify the noise contribution of each individual noise source for a given operating point at any frequency, as shown in the case of noise matching in Fig. 17. As expected, the channel noise is the dominant noise source for the MOSFET. The thermal noise of the resistors can be neglected in this frequency range.

A great advantage of the presented noise model is the ability to determine the noise parameters in dependence of temperature. As an example, Fig. 18 shows a comparison between measurement and simulation of the noise figure  $F_{50}$  at  $50 \Omega$  in dependence of temperature with good agreement.

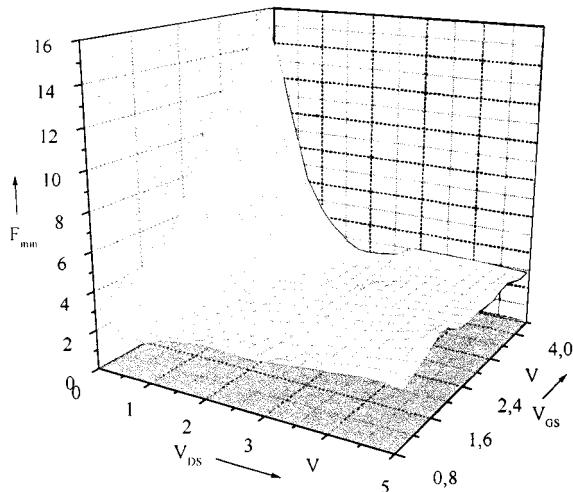

A comparison of measurement and simulation of the minimum noise figure  $F_{\text{min}}$  can be used to show the independence of the operating point of the presented procedure. For this, Fig. 19 shows the measurement of the minimum noise figure  $F_{\text{min}}$  in regard to the operating point.

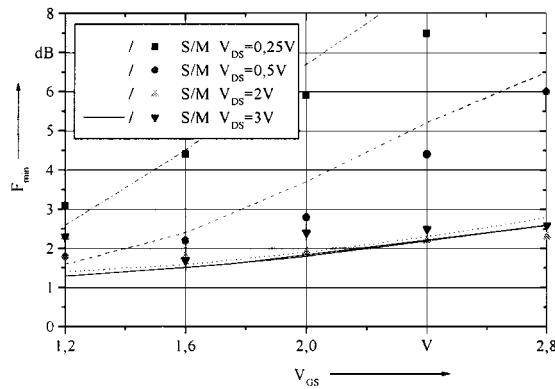

Fig. 20 shows a comparison of measurement and simulation of the minimum noise figure  $F_{\text{min}}$  at different drain-source-voltages  $V_{\text{GS}}$  with good agreement. The maximum deviation is less than 10% both in the triode and saturation regions.

The presented noise model can also be used to derive the absolute noise minimum of a device. Moreover, the noise figure can be extrapolated for higher frequencies. It requires in addition to the small-signal equivalent circuit only one parameter for

Fig. 19. Measured minimum noise figure versus operating point at a temperature of  $T = 293$  K.

Fig. 20. Comparison of the measured minimum noise figure (dots) with simulation (lines) versus operating point at a temperature of  $T = 393$  K.

the channel noise, which can be calculated or measured and can be used easily as a simulation model for computer-aided design (CAD).

## VII. CONCLUSION

A new deembedding procedure for the derivation of the RF equivalent circuit has been described. As a result, a new method for the determination of the gate capacitance and channel resistance is presented. With the use of an open test structure and measurements at different bias conditions, parasitic elements can be determined using analytic equations. The analytic solution for parasitic and intrinsic elements allows the determination of the element values at any specific frequency. The validity of the small-signal equivalent circuits used for the procedure can be checked by examining the frequency dependence of the derived elements. This method allows quick derivation of the intrinsic small-signal equivalent elements for circuit development [10]. Moreover, a temperature noise model based on the small-signal equivalent circuit is presented. For the noise modeling, all intrinsic and parasitic noise contributions of the resistors are taken into account. The only additional noise source represents the channel noise and can be calculated analytically

or measured at any frequency. The noise model can be used to determine the four noise parameters normally used for noise characterization in dependence of temperature, operating point, and frequency. With the knowledge of one noise measurement at a special frequency, even an extrapolation of the noise value versus frequency is possible.

## ACKNOWLEDGMENT

The authors would like to thank E. Gerhardt, Alcatel Company, Stuttgart, Germany, and E. Sailer, Alcatel Company, who provided us with a test wafer from the Jessi Project.

## REFERENCES

- [1] C. E. Biber, M. L. Schmatz, T. Morf, U. Lott, and W. Bächtold, "A nonlinear microwave MOSFET model for SPICE simulators," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 604–610, May 1998.

- [2] H. Cho and D. E. Burk, "A three-step method for the de-embedding of high-frequency  $S$ -parameter measurements," *IEEE Trans. Electron Devices*, vol. 38, pp. 1371–1375, June 1991.

- [3] A. Pascht, M. Grözing, V. Dudek, B. Höfflinger, and M. Berroth, "Parasitic extraction for silicon MOSFETs," presented at the IEEE MTT-S Workshop, Freiburg, Germany, 1998.

- [4] A. Eskandarian and S. Weinreb, "A note on experimental determination of small-signal equivalent circuit of millimeter-wave FETs," *IEEE Trans. Microwave Theory Tech.*, vol. 41, pp. 159–162, Jan. 1993.

- [5] M. Berroth and R. Bosch, "High-frequency equivalent circuit of GaAs FET's for large-signal applications," *IEEE Trans. Microwave Theory Tech.*, vol. 39, pp. 224–229, Feb. 1991.

- [6] M. W. Pospieszalski, "Modeling of noise parameters of MESFET's and MODFET's and their frequency and temperature dependence," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1340–1350, Sept. 1989.

- [7] H. Hillbrand and P. H. Russer, "An efficient method for computer aided noise analysis of linear amplifier networks," *IEEE Trans. Circuits Syst.*, vol. CAS-23, pp. 235–238, Apr. 1976.

- [8] A. van der Ziel, *Noise in Solid State Device and Circuits*. New York: Wiley, 1986.

- [9] B. Wang, J. R. Hellums, and C. G. Sodini, "MOSFET thermal noise modeling for analog integrated circuits," *IEEE J. Solid-State Circuits*, vol. 29, pp. 833–835, July 1994.

- [10] M. Berroth, A. Pascht, J. Fischer, and D. Wiegner, "MOSFET noise model and low noise amplifier design," in *GHz 2000 Symp. Dig.*, Göteborg, Sweden, pp. 367–370.

**Andreas Pascht** was born in Welzheim, Germany, in 1971. He received the Dipl.-Ing. degree from the University of Stuttgart, Stuttgart, Germany, in 1996, and is currently working toward the Ph.D. degree at the Institute of Electrical and Optical Communication Engineering, University of Stuttgart.

His research concerns small-signal and noise modeling of MOS field-effect-transistors and the development of low-noise RF-CMOS circuits.

**Markus Grözing** was born in Reutlingen, Germany, in 1973. He received the Dipl.-Ing. degree from the University of Stuttgart, Stuttgart, Germany, in 2000, and is currently working toward the Ph.D. degree on RF-CMOS circuits at the Institute of Electrical and Optical Communication Engineering, University of Stuttgart.

**Dirk Wiegner** was born in Stuttgart, Germany, in 1975. He is currently working toward the Dipl.-Ing. degree at the Institute for Electrical and Optical Communication Engineering, University of Stuttgart, Stuttgart, Germany.

**Manfred Berroth** (M'91) was born in Obersontheim, Germany, in 1956. He received the Dipl.-Ing. degree from the University of the Federal Armed Forces, Munich, Germany, in 1979.

He then developed microprocessor systems and dedicated image-processing software as a Consultant. In 1987, he joined the Institute for Applied Solid State Physics, Freiburg, Germany, where he was engaged in the development of circuit simulation models for GaAs field-effect transistors, as well as integrated circuit design. Since 1996, he has been a Professor with the Institute for Electrical and Optical Communication Engineering, University of Stuttgart, Stuttgart, Germany. His research interests and activities are electronic and optoelectronic devices and circuits at high frequencies.